# **Software Architecture of Microprocessors and Microcontrollers**

| Chapter 1 | Overview                                                   |

|-----------|------------------------------------------------------------|

| Chapter 2 | Architecture of a typical Microcontroller: Freescale HCS12 |

| Chapter 3 | Peripherals, Input/Output, Interrupts                      |

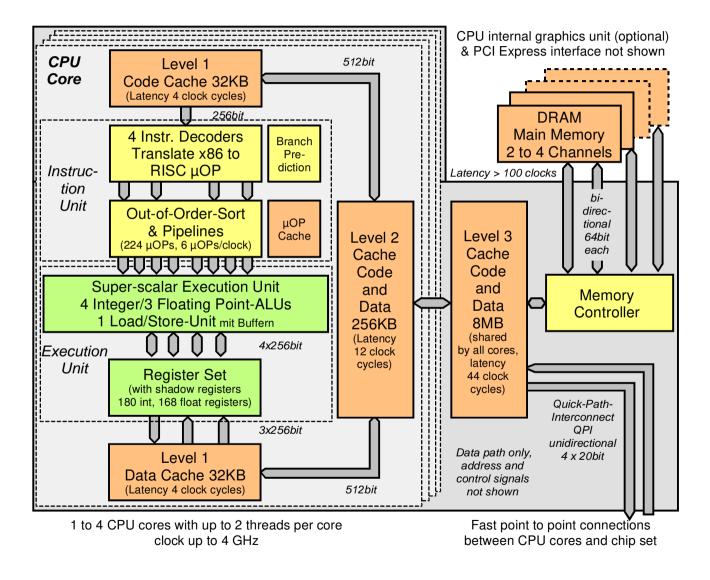

| Chapter 4 | Modular Programming in C and Assembler                     |

| Chapter 5 | Advanced Microprocessor Architectures Intel x86 - ARM      |

|           |                                                            |

| Lab 1     | HCS12 Assembler Programming                                |

| Lab 2     | Clock - HCS12 Interrupts and Input-/Output                 |

| Lab 3     | Radio-controlled Clock with DCF77 Interface                |

Webpage and Link to Moodle Course CA-SWB4-TIB4:

www.hs-esslingen.de/

Prof. Dr. rer. nat (Purdue Univ.) Jörg Friedrich

mitarbeiter/Werner-Zimmermann

Prof. Dr.-Ing. Werner Zimmermann

Aktuelle Vorlesungen – Computerarchitektur

Prof. Dr.-Ing. Werner Zimmermann

Hochschule Esslingen – University of Applied Sciences – Department of Information Technology

#### **Computer Architecture**

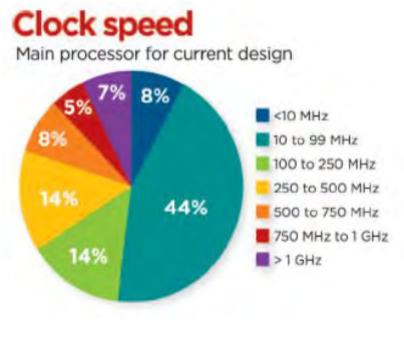

This is how a computer looks like

....

... or like

This "gas" station is based on a **computer too!**

And some computers even make it into the news ....

#### **IT World Champions ...**

... and finally Europe

1.4

#### **Computer Architecture**

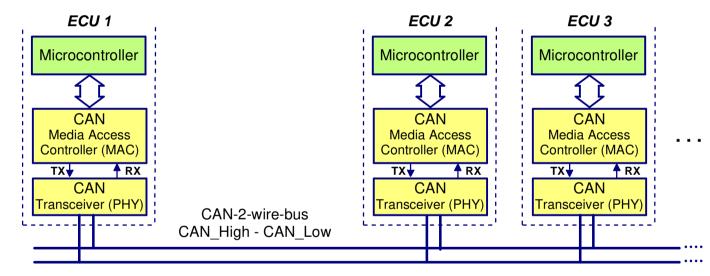

# The Embedded World: Automotive, Industrial & Home Automation, Medical Systems

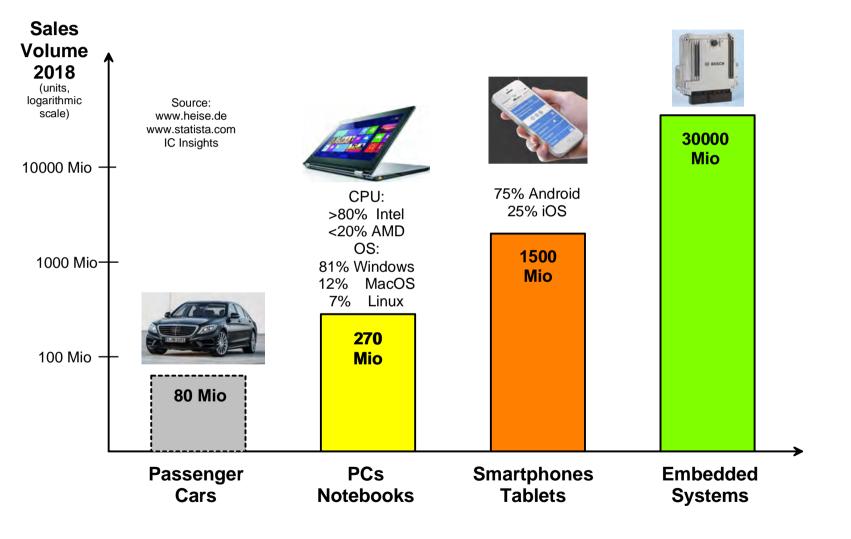

# How important is it?

## ... more to come: Internet of Things IoT Everything will be a computer on a global network

#### **Wearables**

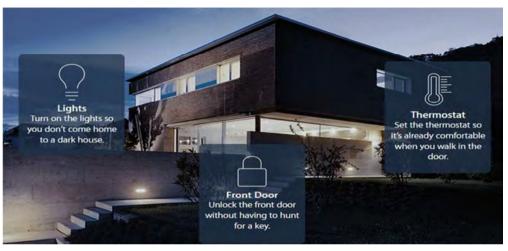

**Home Automation**

#### **Automated Cars**

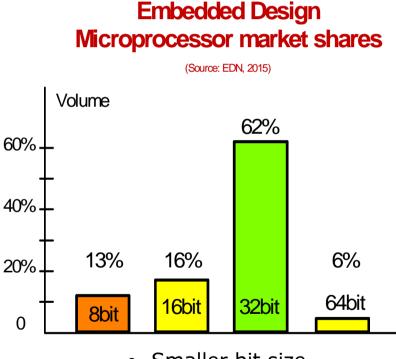

# What is special with embedded systems?

- **Reliability and safety** a major issue  $\rightarrow$  buggy software can kill people

- **Real time** requirements

- **Resource constraints**

- $\rightarrow$  computer must run in sync with external events

- $\rightarrow$  computing speed and memory size matter (cost!)

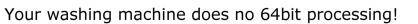

Smaller bit size

Moderate clock speed

It is not the CPU's job to heat your toaster!

Sources: www.embedded.com, ESD Market Survey; Michael Barr, Real men program in C, www.embedded.com. Statista.com

# Most popular Programming Languages

|                   | Typical Application                 | TIOBE Rating | IEEE Rank |

|-------------------|-------------------------------------|--------------|-----------|

| С                 | General Purpose                     | 16%          | 3         |

| C++               | General Purpose                     | 7%           | 4         |

| Java              | Business Applications, Android Apps | 13,5%        | 2         |

| Python            | Numerical Analysis, AI, Testing     | 10,5%        | 1         |

| C#                | General Purpose                     | 4,5%         | 7         |

| Visual Basic      | Business Application                | 4%           | -         |

| Javascript        | Web Clients and Servers             | 2,5%         | 6         |

| PHP               | Web Servers                         | 2,5%         | -         |

| SQL               | Database                            | 2%           | -         |

| Objective C+Swift | Apple IOS Apps                      | 2%           | 9         |

| R                 | Numerical Analysis                  | 2%           | 5         |

| Matlab            | Numerical Analysis                  | 1%           | 8         |

| Assembler         | Performance Sensitive Applications  | 1%           | -         |

| Ruby, Rust, Go,   |                                     | je < 1%      | -         |

|                   |                                     |              |           |

|                   |                                     | Total 100%   | Top 10    |

Sources (as of Sept 2020)

a) <u>https://www.tiobe.com/tiobe-index/</u>

b) <u>https://spectrum.ieee.org/computing/software/the-top-programming-languages-2019</u>

c) https://www.ahl.com/ahl-tech-the-curious-case-of-the-longevity-of-c

#### Large or small ...

Smartphone

Automotive Electronic Control Unit

Main Frame

PC

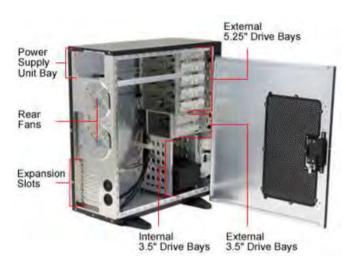

# ... all computers have the same basic structure

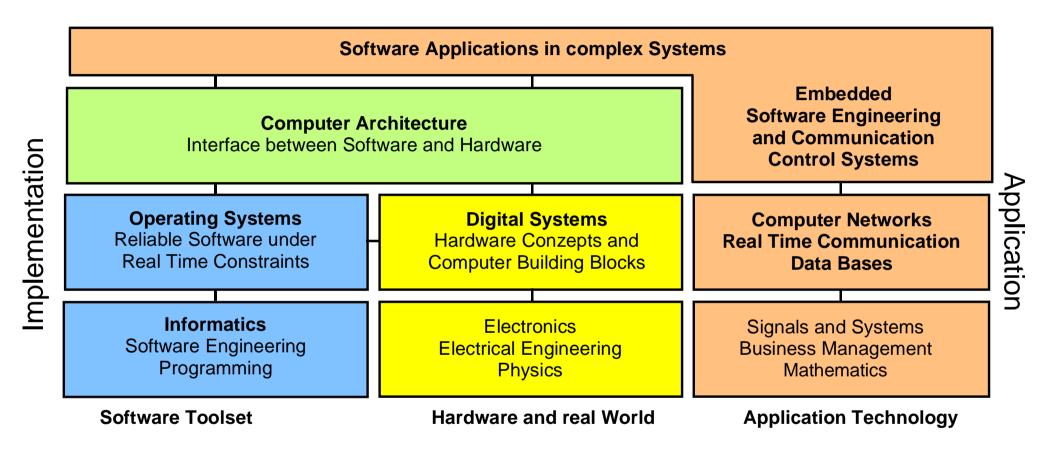

# What do you need to know: Our IT curriculum

#### Literature

The following list is a small selection out of a large range of books about computer architecture, microprocessors and microcontrollers:

#### **Introductory Books**

Computer Architecture and Organization

| [1.1] | Patterson, D.; Hennessy,<br>J.:                                    | Computer Organization and Design. Hardware-/Software-Interface.<br>Morgan Kaufmann Publishers<br>(Deutsche Übersetzung: Rechnerorganisation und –entwurf. Spektrum<br>Akademischer Verlag) |

|-------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1.2] | Hennessy, J.; Patterson,<br>D.:                                    | Computer Architecture. A Quantitative Approach. Academic Press<br>(Advanced topics from the same authors as [1.1])                                                                         |

| [1.3] | Tanenbaum, A.:                                                     | Structured Computer Organization. Prentice Hall (<br>(Deutsche Übersetzung: Computerarchitektur. Pearson)                                                                                  |

| [1.4] | Keller, R.; Lindermeir, W.;<br>Marchthaler, R. Zimmer-<br>mann, W. | Digitaltechnik 1 + 2. Vorlesungsskript. Hochschule Esslingen                                                                                                                               |

| [1.5] | Friedrich, J.:                                                     | Echtzeitsysteme – Vorlesungsskript. Hochschule Esslingen                                                                                                                                   |

| [1.6] | Lewis, D.:                                                         | Fundamentals of Embedded Software – Where C and Assembly Meet.<br>Prentice Hall Verlag                                                                                                     |

| [1.7] | Beierlein, Hagenbruch:                                             | Taschenbuch Mikroprozessortechnik. Fachbuchverlag Leipzig                                                                                                                                  |

| Micro | controllers                                                        |                                                                                                                                                                                            |

HCS12 Microcontroller Hardware and Software

| [2.1] | Friedrich, J.:          | Computerarchitektur 3 - Vorlesungsskript. Hochschule Esslingen    |

|-------|-------------------------|-------------------------------------------------------------------|

| [2.2] | Kreidl, H.; Kupris, G.; | Mikrocontroller-Design. Hardware- und Softwareentwicklung mit dem |

|       | Thamm, O.:              | 68HC12/HCS12. Hanser Verlag                                       |

| [2.3] | Huang, H.W.:            | The HCS12/9S12. An Introduction to Hardware and Software Interfa- |

|       |                         | cing. Thomson Learning                                            |

| [2.4] | Barret, S.; Pack, D.: | Embedded Systems: Design and Applications with the 68HC12 and                                                                     |

|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|       | Cody F                | HCS12. Prentice Hall                                                                                                              |

| [2.5] | Cady, F.:             | Software and Hardware Engineering: Assembly and C-Programming for<br>the Freescale HCS12 Microcontroller. Oxford University Press |

|       |                       |                                                                                                                                   |

| [2.6] | Almy, T.:             | Designing with Microcontrollers: The 68HCS12. Buchtext auf CD.                                                                    |

|       |                       | http://www.hcs12text.com                                                                                                          |

#### Data Books

*Freescale HCS12 Datasheets from http://www.freescale.com/webapp/sps/site/prod\_summary.jsp?code=MC9S12DP256B#Data\_Sheets*

| [3.0] | Freescale | Microcontroller MC9S12DP256 All-in-one-manual (outdated): 000-MC9S12DP256.pdf                   |

|-------|-----------|-------------------------------------------------------------------------------------------------|

| [3.1] | Freescale | CPU-Architecture, Instruction Set, Operand Addressing:<br>001-S12CPUV2-ReferenceManual.pdf      |

| [3.2] | Freescale | Microcontroller MC9S12DP256B Peripherals Overview:<br>002-9S12DP256BDGV2-DevicesUserGuide.pdf   |

| [3.3] | Freescale | Digital-I/O, Interrupt System:<br>003-S12DP256PIMV2-Port Integration Module.pdf                 |

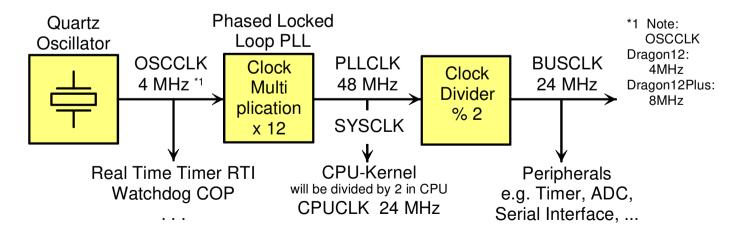

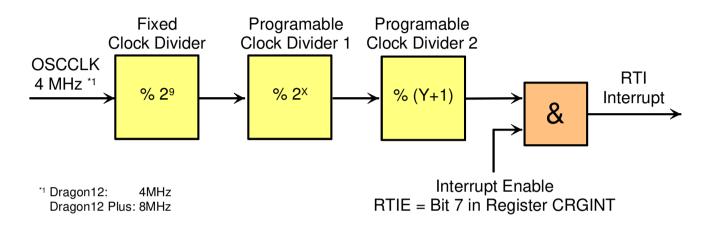

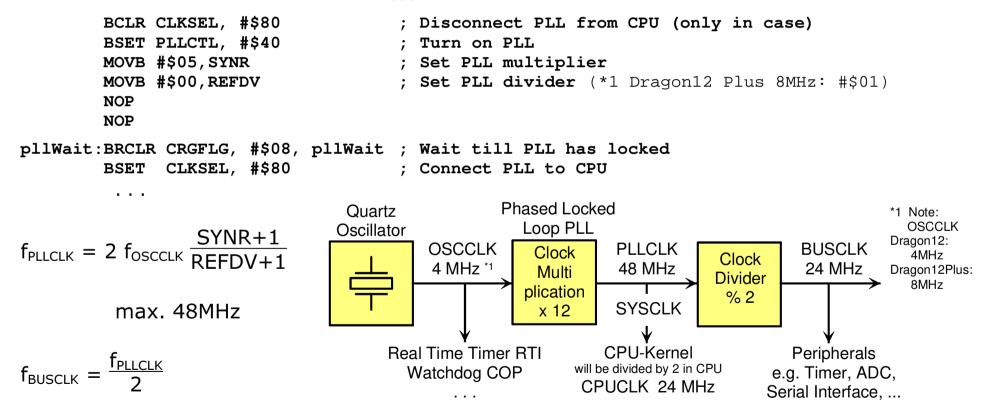

| [3.4] | Freescale | Clock and Reset Generator, Real Time Interrupt:<br>004-S12CRGV2-Clock&Reset-Generator.pdf       |

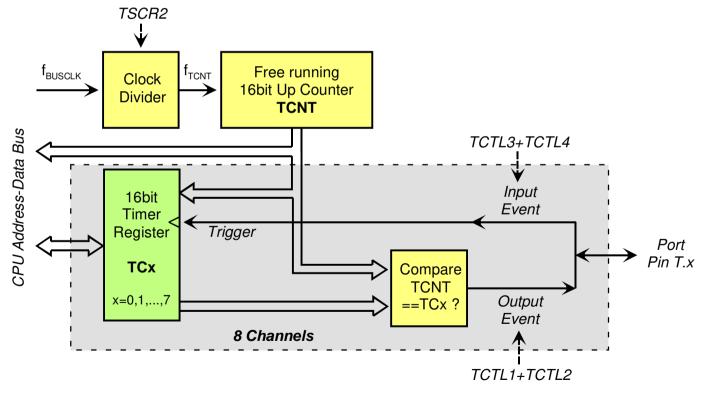

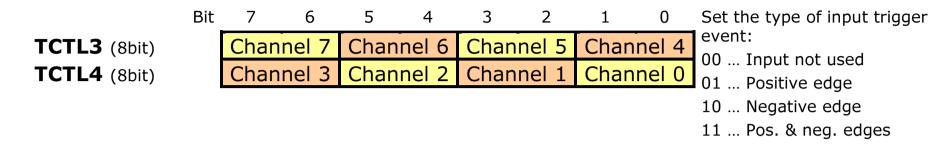

| [3.5] | Freescale | Timer and Capture/Compare Inputs/Outputs:<br>005-S12-ECT_16B8CV1-Enhanced Capture Timer.pdf     |

| [3.6] | Freescale | Serial Interface:                                                                               |

| [3.7] | Freescale | 006-S1-2SCIV2-Serial Communication Interface.pdf<br>PWM-Outputs:                                |

| [3.8] | Freescale | 007-S12PWM_8B8CV1-PWM.pdf<br>Analog-Digital-Converter:<br>008-S12ATD10B8CV2-AnalogToDigital.pdf |

#### Literature

| [3.9]  | Freescale            | CAN-Interface:<br>009-S12MSCANV2-CAN.pdf                                                                |

|--------|----------------------|---------------------------------------------------------------------------------------------------------|

| [3.10] | Freescale            | Port A, B, E, K und Multiplex-Address-Data Bus<br>010-S12MEBIV3.pdf                                     |

| [3.11] | Wytec/EVBplus        | Dragon12 MC9S12DP256 Development Board. Getting Started Manual<br>and Circuit Diagrams. www.evbplus.com |

| [3.12] | Freescale/Metroworks | Codewarrior Development Studio IDE User's Guide.<br>8_16bit_IDE_Users_Guide.pdf                         |

| [3.13] | Freescale/Metroworks | HC12/S12 Compiler. Compiler_HC12.pdf                                                                    |

| [3.14] | Freescale/Metroworks | HC12/S12 Assembler Manual. Assembler_HC12.pdf                                                           |

| [3.15] | Freescale/Metroworks | Codewarrior Debugger. Debugger_HC12.pdf                                                                 |

|        | Freescale/Metroworks | HC12/S12 True Time Simulator. See [3.15]                                                                |

| [3.17] | Freescale/Metroworks | Linker. Build_Tools_Utilities.pdf                                                                       |

#### Acknowledgements

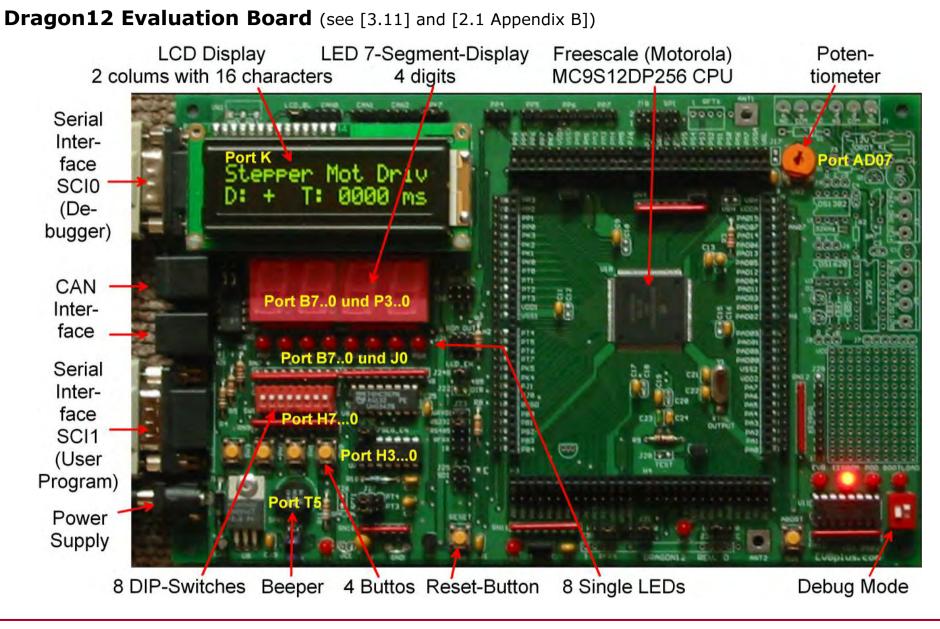

The HCS12 microcontroller and the Dragon12 evaluation board were introduced by Prof. Dr. J. Friedrich (see [2.1]). Good job, thanks.

#### W. Zimmermann

# Chapter 2 Architecture of a typical Microcontroller: Freescale HCS12

| 2.1 | Basic Features of Microcontroller Family HCS12           | 2    |

|-----|----------------------------------------------------------|------|

| 2.2 | Hello Embedded World                                     | 7    |

| 2.3 | Register Model, Data Types, Addressing Modes             | 15   |

| 2.4 | Instruction Set 1: Data Transport                        | . 22 |

| 2.5 | Instruction Set 2: Arithmetic and Logic Operations       | . 28 |

| 2.6 | Instruction Set 3: Compare and Branch                    | .34  |

| 2.7 | Instruction Set 4: Subroutine Calls and State Management | 40   |

| 2.8 | Stack                                                    | 43   |

| 2.9 | Instruction Size and Execution Speed                     | .46  |

|     |                                                          |      |

Appendix: CodeWarrior HCS12 Development Environment

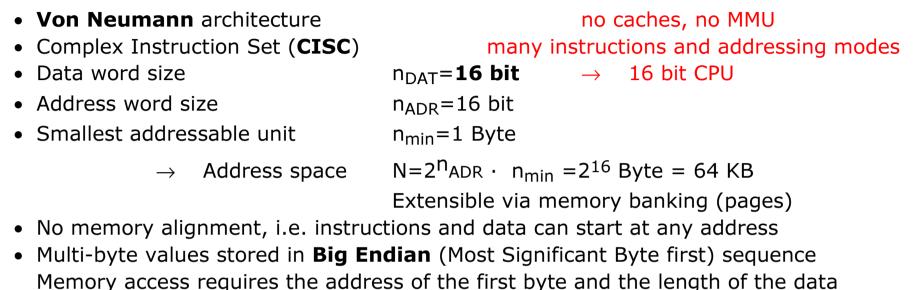

# **2.1 Basic Features of Microcontroller Family HCS12**

# 2.1 Basic Features of Microcontroller Family HCS12

Example: 16bit value \$4433 at address \$0103

\*1 Motorola/Freescale use \$... instead of ... h or 0x... to mark hexadecimal values, e.g. \$4433 = 4433h

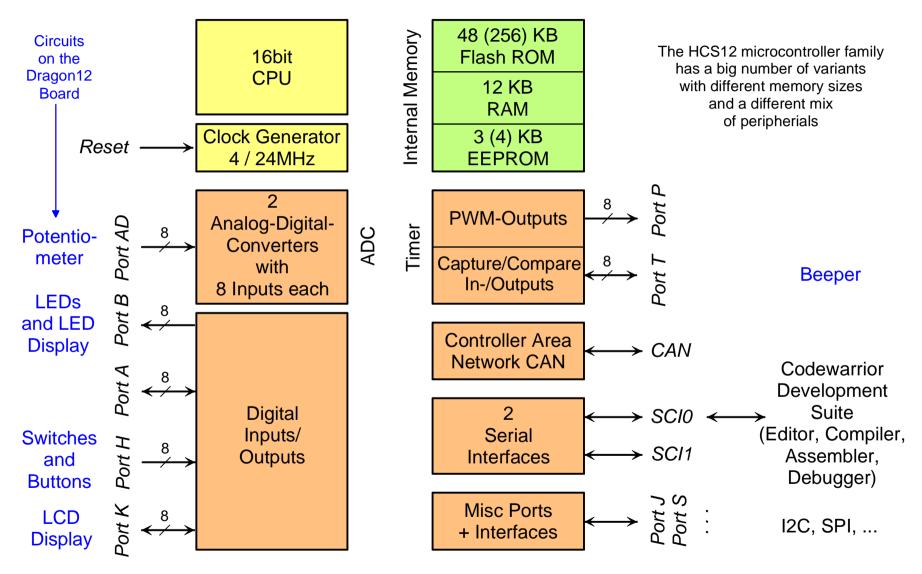

# Block Diagram of Microcontroller MC9S12DP256 (see [3.0 Page 16], [3.2 Fig. 1-1])

# **2.1** Basic Features of Microcontroller Family HCS12

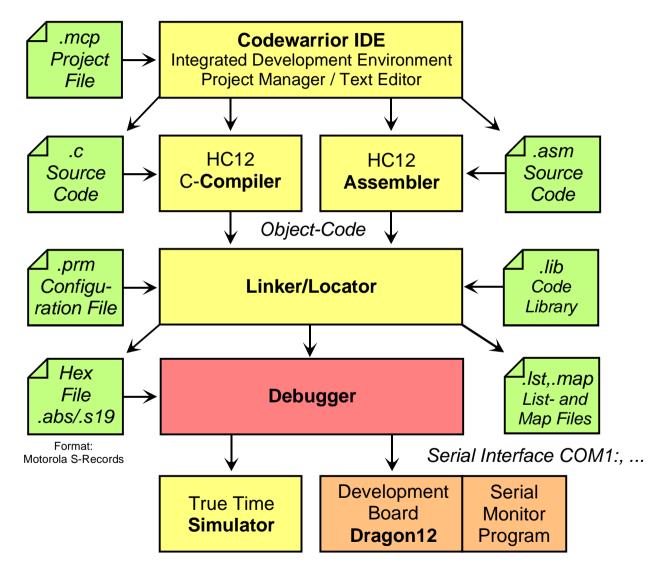

Integrated Development Environment (IDE) Freescale CodeWarrior (see [3.12 - 3.17])

Historical Note: Semiconductor manufacturer Freescale in former times was part of Motorola. The CodeWarrior tools were developed by Metroworks, which was purchased by Freescale.

# MC9S12DP256 Memory Map (see [3.0 Page 120], [3.2 Fig. 1-2])

The HCS has several operating modes. In the lab we use the Normal Single Chip Mode without external memory.

| \$0000 | HW/SW Interface: Registers to<br>control the On-Chip-Peripherals 1KB | All peripherals are Memory-Mapped, i.e. for software their registers look like variables                                                                             |

|--------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$0400 | EEPROM 3KB                                                           | The EEPROM has 4KB, but 1KB is shadowed by the peripheral registers.                                                                                                 |

| \$1000 | RAM<br>12KB                                                          | Program variables<br>Stack for debug monitor program at the end<br>of the RAM area (36B)                                                                             |

| \$4000 | Flash-ROM<br>16KB                                                    | Program code                                                                                                                                                         |

| \$8000 | Flash-ROM<br>16KB                                                    | This address range can be used to map ad-<br>ditional 16KB Flash-ROM pages (Page Win-<br>dow selected by PPAGE-register) $\rightarrow$ Memory<br>extension to > 64KB |

| \$C000 | Flash-ROM<br>16KB                                                    | \$F780 \$FE00:<br>Debugger Monitor Program                                                                                                                           |

| \$FFFF |                                                                      | \$FF00 \$FFFF:<br>Interrupt Vector Table 256B                                                                                                                        |

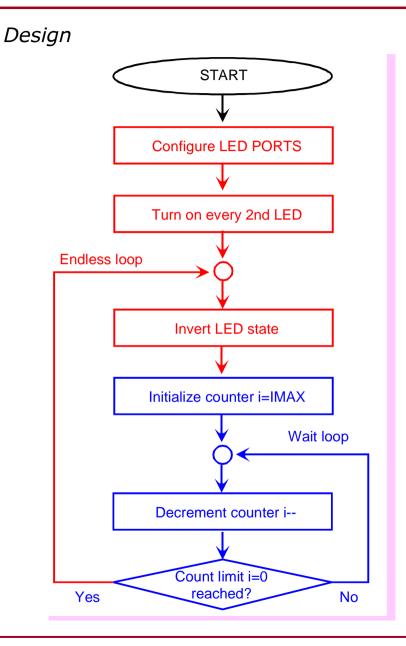

# 2.2 Hello Embedded World

# 2.2 Hello Embedded World

Ever since Kernighan and Ritchie in their book "The C Programming Language", the first program to introduce a programing language used to be "**Hello World**", which outputs a short text string to the display. However, typical embedded systems don't have a keyboard and a display. So the idea is modified and digital output pins are toggled (**Toggle Port**), to which LEDs are connected (**Blinking LEDs**).

Converting the idea into a running program on the Dragon12 board takes some steps:

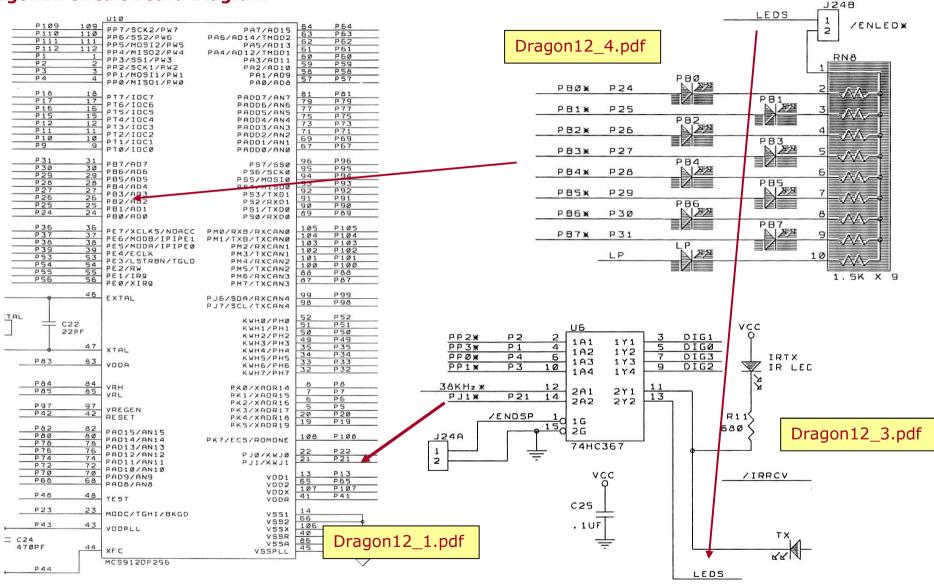

# Step 1: What is the hardware setup of the evaluation board?

Where are the LEDs connected and how can they be controlled?

| Info source<br>[3.11]:                                                          | ON-BOARD HARDWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Getting_started<br>_Dragon12.pdf<br>S.11<br>Port J.1<br>Output<br>J.1= 0 Enable | Each port B line is monitored by a LED. It works OK in single chip mode. In order to turn on port B LEDs, the PJ1 (pin 21 of MC9S12DP256) must be programmed as output and set for logic zero. If the board is used in expanded mode, the port B becomes the address/data bus, AD0-AD7, and the LEDs will add too much load on the bus. In order to make it work in expanded mode, J24A and J24B must be removed to disable the 7-segment LED display and the PB0-PB7 LEDs. |

| LED<br>Port B.7 0<br>Outputs<br>B.x=1 $\rightarrow$ LED<br>on                   | Port A is used as the 4X4 keypad interface in single chip mode, but in expanded mode, port A becomes the address/data bus AD8-AD15 and it cannot be connected with a keypad.<br>Port H is connected to an 8-position DIPswitch. The DIPswitch is connected to GND via the RN9 (eight 4.7K resistors), so it's not dead short to GND. When port H is programmed as an output port, the DIPswitch setting is ignored.                                                         |

#### **Dragon12 Circuit Board Diagram**

ca3b.docx VZ6.2 Jan 21 © Prof. J. Friedrich, W. Zimmermann, Hochschule Esslingen

**Computer Architecture**

# 2.2 Hello Embedded World

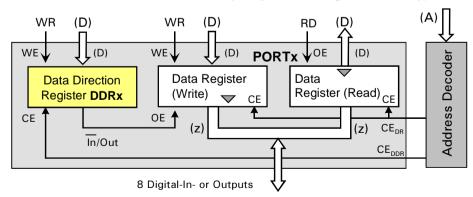

#### Step 2: Hardware setup of the microcontroller

Where are the I/O ports in the CPU's memory address range and how to program them?

#### HCS12 docu 000-MC9S12DP256.pdf [3.0]: Register Map pg.66ff and pg.129ff Input/Output Registers

| PORTB — Port B Register |                            |                 |                 |                 |                 |                 |                 |                 |  |

|-------------------------|----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|

| Address Offse           | et: \$0001                 |                 |                 |                 |                 |                 |                 |                 |  |

|                         | Bit 7                      | 6               | 5               | 4               | 3               | 2               | 1               | Bit 0           |  |

| Single Chip             | Bit 7                      | 6               | 5               | 4               | 3               | 2               | 1               | Bit 0           |  |

| Reset:                  | Reset: Unaffected by reset |                 |                 |                 |                 |                 |                 |                 |  |

| Expanded<br>& Periph:   | ADDR7/<br>DATA7            | ADDR6/<br>DATA6 | ADDR5/<br>DATA5 | ADDR4/<br>DATA4 | ADDR3/<br>DATA3 | ADDR2/<br>DATA2 | ADDR1/<br>DATA1 | ADDR0/<br>DATA0 |  |

| Expanded<br>narrow      | ADDR7                      | ADDR6           | ADDR5           | ADDR4           | ADDR3           | ADDR2           | ADDR1           | ADDR0           |  |

Port B bits 7 through 0 are associated with address lines A7 through A0 respectively and data lines D7 through D0 respectively. When this port is not used for external addresses, such as in single-chip mode,

these pins can be used as general purpose I/O. Data Direction Register B (DDRB) determines the primary direction of each pin. DDRB also determines the source of data for a read of PORTB.

This register is not in the on-chip map in expanded and peripheral modes.

CAUTION: To ensure that you read the value present on the PORTB pins, always wait at least two cycles after writing to the DDRB register before reading from the PORTB register.

Read and write: anytime (provided this register is in the map).

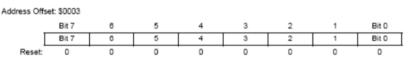

DDRB — Port B Data Direction Register

This register controls the data direction for Port B. When Port B is operating as a general purpose I/O port, DDRB determines the primary direction for each Port B pin. A "1" causes the associated port pin to be an output and a "0" causes the associated pin to be a high-impedance input. The value in a DDR bit also affects the source of data for reads of the corresponding PORTB register. If the DDR bit is zero (input) the buffered pin input is read. If the DDR bit is one (output) the output of the port data latch is read.

This register is not in the on-chip map in expanded and peripheral modes. It is reset to \$00 so the DDR does not override the three-state control signals.

Read and write: anytime (provided this register is in the map).

#### DDRB7-0 — Data Direction Port B

- 0 = Configure the corresponding I/O pin as an input

- 1 = Configure the corresponding I/O pin as an output

# Data register PORTB at address \$0001 Bit PB.x=1 $\rightarrow$ Port pin x = High

# Data direction register DDRB at \$0003 Bit DDRB.x=1 $\rightarrow$ Port pin x as output

Same concept for PORT J Data register PTJ at address \$0268 Data direction register DDRJ at address \$026A

# 2.2 Hello Embedded World

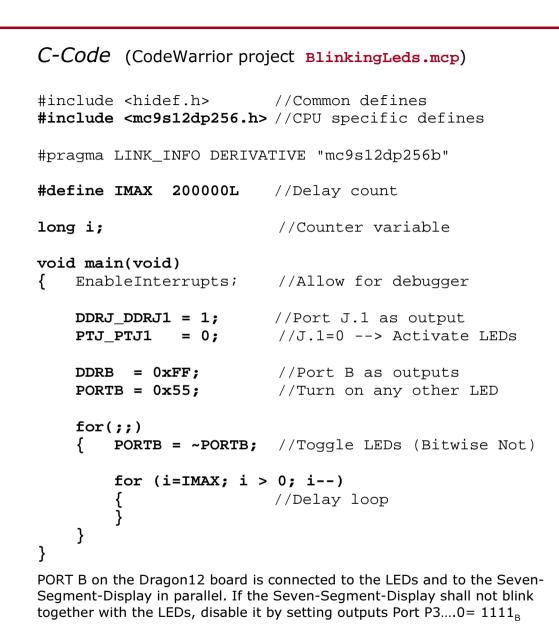

# Step 3: Development environment, program design and coding

How do I write and compile a program?

# • Installation and use of the IDE see Appendix CodeWarrior

• To simplify coding, instead of using hexadecimal addresses the IDE comes with include files defining symbols for registers and their respective bit positions, e.g.

| Predefined Symbols in<br>Include-Files for |             | for C-Programs <sup>*1</sup><br>mc9s12dp256.h | for Assembler-Programs<br>mc9s12dp256.inc |

|--------------------------------------------|-------------|-----------------------------------------------|-------------------------------------------|

| Port B:                                    | Port        | <pre>#define PORTB (*(char*) 0x0001)</pre>    | PORTB: equ \$0001                         |

|                                            | PORTB Bit 0 | #define <b>PORTB_BIT0</b> PORTB.Bits.BIT0     |                                           |

|                                            |             |                                               |                                           |

|                                            | DDRB        | <pre>#define DDRB (*(char*) 0x0003)</pre>     | <b>DDRB:</b> equ \$0003                   |

|                                            | DDRB Bit 0  | #define <b>DDRB_BIT0</b> DDRB.Bits.BIT0       |                                           |

| Port J:                                    | Port        | #define <b>PTJ</b> (*(char*) 0x0268)          | <b>PTJ:</b> equ \$0268                    |

|                                            | PTJ Bit 0   | #define <b>PTJ_PTJ0</b> PTJ.Bits.PTJ0         |                                           |

|                                            |             |                                               |                                           |

|                                            | DDRJ        | <pre>#define DDRJ (*(char*) 0x026A)</pre>     | DDRJ: equ \$026A                          |

| •                                          | DDRJ Bit 0  | #define <b>DDRJ_DDRJ0</b> DDRJ.Bits.DDRJ0     |                                           |

Simplified, actually ports are described via C-structures and unions of bit fields and byte or word-data types. Unfortunately, naming conventions for ports are not unified (PORTB, but PTJ)

### Step 4: Debug environment

How to download a program to the board and debug it?  $\rightarrow$  see Appendix CodeWarrior

**Computer Architecture**

#### Memory Requirements of the C-Program (see file simulator.map)

| Summary of section s | izes per section type: |                                                                    |

|----------------------|------------------------|--------------------------------------------------------------------|

| READ_ONLY (R):       | 9B (dec: 155)          | ← ROM: Program code + constant data                                |

| READ_WRITE (R/W):    | 104 (dec: 260)         | $\leftarrow$ RAM: Variable data 4 Byte (+ Stack 256 Byte $^{*1}$ ) |

| NO_INIT (N/I):       | 23D (dec: 573)         | $\leftarrow$ Peripheral registers (fixed for all programs)         |

The C-compiler does not generate the most efficient code here. By manually programming in machine language (assembler code) rather than C, a faster and smaller program is possible (see next page):

| Summary of section s | sizes per section type: |                                                                          |

|----------------------|-------------------------|--------------------------------------------------------------------------|

| READ_ONLY (R):       | 2A (dec: 42)            | ← ROM: Program code + constant data                                      |

| READ_WRITE (R/W):    | 100 (dec: 256)          | $\leftarrow$ RAM: Variable data 0 Byte (+ Stack 256 Byte <sup>*1</sup> ) |

#### Execution Speed (measured with HCS12 simulator)

| Run time in CPU clock ticks             | C-Program | Assembler-Program |

|-----------------------------------------|-----------|-------------------|

| CPU Reset to line Toggle LEDs           | 99 clocks | 19 clocks         |

| 1 loop cycle Toggle LEDs to Toggle LEDs | 47 clocks | 17 clocks         |

Here the stack size could have been reduced even with the C-program. The assembler program could have been implemented completely without stack, if no debugging was required (the debug monitor uses the stack)

→ To understand, how to optimize high level language programs for embedded systems for size and speed (and to be able to find bugs in development tools like compilers and libraries) knowledge of assembler language programming is required.

# Blinking LEDs in optimized HCS12 Assembler (CodeWarrior project BlinkingLedsAsm.mcp)

| XDEI<br>XREI<br>INCI   |                                                                             | ; Export symbols<br>; Import symbols: End of stack<br>; include derivative specific macros                                                                                                                                                            |

|------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IMAX: EQU<br>.data:    | J 2048<br>SECTION                                                           | ; Symbolic constant: Delay count<br>; RAM: Variable data section (not used in this program)                                                                                                                                                           |

| .const:                | SECTION                                                                     | ; ROM: Constant data (not used in this program)                                                                                                                                                                                                       |

| .init:                 | SECTION                                                                     | ; ROM: Code section                                                                                                                                                                                                                                   |

| <b>main:</b><br>Entry: | LDS #SEG_END_SSTACK<br>CLI                                                  | ; <b>Begin of the program</b><br>; Initialize stack pointer<br>; Enable interrupts, needed for debugger                                                                                                                                               |

|                        | BSET DDRJ, #2<br>BCLR PTJ, #2                                               | <pre>; Bit Set: Port J.1 as output ; Bit Clear: J.1=0&gt; Activate LEDs</pre>                                                                                                                                                                         |

|                        | MOVB #\$FF, DDRB<br>MOVB #\$55, PORTB                                       | <pre>; \$FF -&gt; DDRB: Port B.70 as outputs (LEDs) ; \$55 -&gt; PORTB: Turn on every other LED</pre>                                                                                                                                                 |

| loop:                  | COM PORTB                                                                   | ; Complement Port B:Toggle LEDs                                                                                                                                                                                                                       |

| waitO:<br>waitI:       | LDX #IMAX<br>LDY #IMAX<br>DBNE Y, waitI<br>DBNE X, waitO<br><b>BRA loop</b> | <pre>; Delay loop to control toggle Frequency<br/>; (Uses two nested counter loops with registers X and Y)<br/>; Decrement Y and branch to waitI if not equal to 0<br/>; Decrement X and branch to wait0 if not equal to 0<br/>; Branch to loop</pre> |

|                        | DRA TOOD                                                                    | j Branch to 100p                                                                                                                                                                                                                                      |

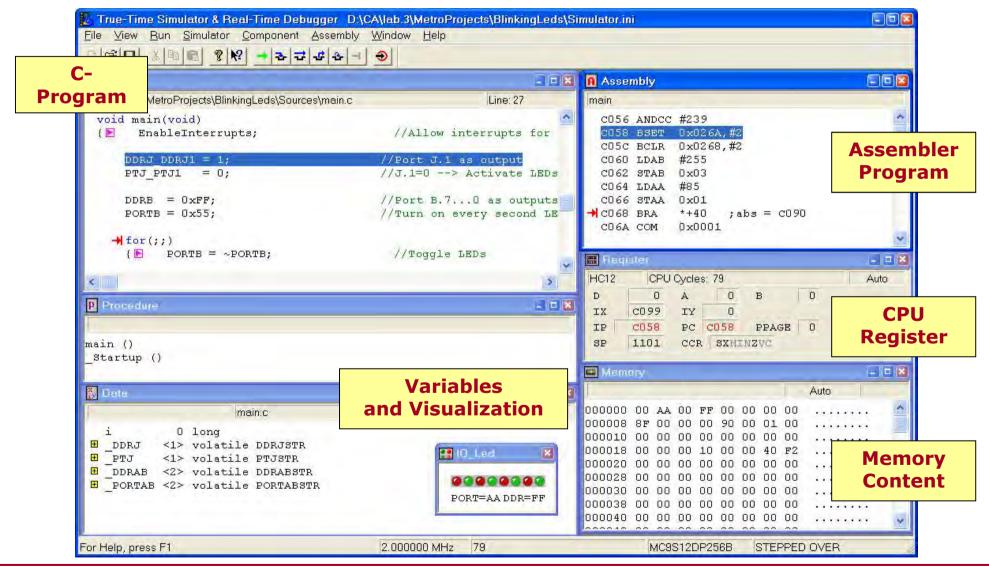

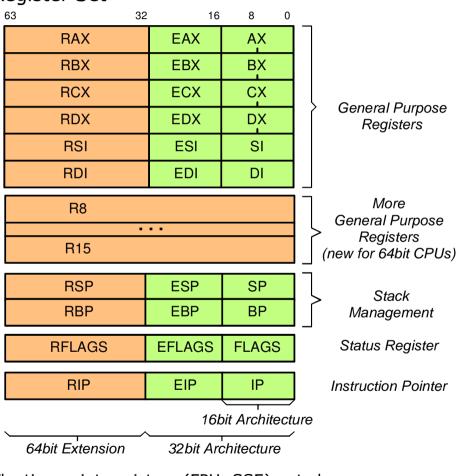

2.3 Register Model (registers accessible for assembler programs, see [3.1 Chapter 2])

#### Accumulator

16 bit register D, can be used in two halves as two 8 bit registers A and B for arithmetic-logic operations

| Index Register X                                                                                           | data and/or pointers                              |  |  |  |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| Index Register Y                                                                                           | data and/or pointers                              |  |  |  |

| Stack Pointer SP                                                                                           | pointer to stack                                  |  |  |  |

| Program Counter PC                                                                                         | address of next instruction (Instruction Pointer) |  |  |  |

| <b>Condition Code Register</b> (status register)<br>Status bits for arithmetic operations and control bits |                                                   |  |  |  |

| CCR-Register Details                                                                                       |                                                   |  |  |  |

| Overflow for operations wit                                                                                | h unsigned operands                               |  |  |  |

| Overflow for signed operan                                                                                 | ds (two's complement)                             |  |  |  |

| Operation result is null                                                                                   |                                                   |  |  |  |

| Operation result is negative                                                                               | e                                                 |  |  |  |

| Disable on-chip interrupt signals (Reset: I=1)                                                             |                                                   |  |  |  |

| Overflow for operations with BCD-numbers                                                                   |                                                   |  |  |  |

Disable external interrupt signals (Reset: X=1) Ignore stop command (State after CPU reset: S=1)

# **Data Types**

|                                                                 |                                                                                                             | S12                          | 80x86                           |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------|--|--|

|                                                                 | Assembler *1                                                                                                | HCS12 C <sup>*1</sup>        | Visual C++                      |  |  |

|                                                                 | <ul> <li>Natural numbers (unsigned) <sup>*2</sup></li> <li>Whole numbers (signed, 2s-complement)</li> </ul> |                              |                                 |  |  |

| 8bit -128 +127<br>0 255                                         | DC.B, DS.B <sup>*3</sup><br>(byte)                                                                          |                              | ar<br>yned char                 |  |  |

| 16bit –32768 +32767<br>0 65535                                  | DC.W, DS.W *3<br>(word)                                                                                     | short, int<br>unsigned short | short<br>unsigned short         |  |  |

| 32bit -2147483648+2147483647<br>0 4294967295                    | DC.L, DS.L *3<br>(long, dword)                                                                              | long<br>unsigned long        | int, long<br>unsigned int, long |  |  |

| <ul> <li>Floating-point numbers</li> </ul>                      |                                                                                                             |                              |                                 |  |  |

| IEEE 32bit                                                      | -                                                                                                           | float, double $*^1$          | float                           |  |  |

| IEEE 64bit                                                      | -                                                                                                           | (double) <sup>*1</sup>       | double                          |  |  |

| <ul> <li>Addresses/Pointers<br/>(for all data types)</li> </ul> | 16bit<br>(near pointer)                                                                                     | 16bit<br>(near pointer)      | 32bit or 64bit                  |  |  |

| Bit field                                                       | 1bit                                                                                                        | 8, 16 or 32bit               | 32bit                           |  |  |

| Enumeration                                                     | -                                                                                                           | 16bit                        | 32bit                           |  |  |

| Array                                                           | *3 datatype name[count]                                                                                     |                              | name[count]                     |  |  |

| Structure, union                                                | -                                                                                                           | struc                        | ct, union                       |  |  |

| _               |           |                       |                    |

|-----------------|-----------|-----------------------|--------------------|

|                 |           | HCS12 Assembler       | С                  |

| Decimal         | (Base 10) | -34,                  | 127                |

| Hexadecimal     | (Base 16) | \$3F8A , -\$3F        | 0x3F8A             |

| Octal           | (Base 8)  | @7345                 |                    |

| Dual            | (Base 2)  | %10101001             | 0b10101001         |

| Floating-point  |           | -                     | 3.14159 , 1.6e-19  |

| ASCII character |           | 'Z'                   | 'Z'                |

| ASCIIZ string   | *4        | "This is a string", 0 | "This is a String" |

# **Coding of Numbers and String Constants**

\*1

\*3

The bit size of most data types can be configured via HCS12 C-compiler options.

\*2 Assembler does not make a difference between signed and unsigned data.

Variable in RAM-memory: name: DS.B count

defines 8bit variables in RAM-memory, which can be used via their name. The variables will **not** be initialized. Use count > 1 to define an array. Use ps.w and ps.L to define 16bit or 32bit variables and arrays.

Constant in ROM-memory: name: DC.B value

defines 8bit constants in ROM-memory, which can be used via their name. The constant will be initialized to value Use DC.w and DC.L to define 16bit and 32bit constants.

Use

to define a block of constants with count bytes and initialize each byte to value. Same with DCB.W and. DCB.L.

name: DCB.B count, value

\*4

In C the end of a string will automatically be marked with a 0-byte (ASCII Zero String). In Assembler the 0byte must be specified explicitly.

**Operand Address Modes** (see [3.1 Chapter 3], [1.4 Chapter 4], [2.1 Chapter 2.7])

HCS12 is a **Two-Address-CPU**, i.e. a CPU instruction can have up to two operands. One of the operands (destination operand) will be overwritten by the instruction's result:

Register operands

### in C/C++ in HCS12-ASM

| (Explicit)<br>Register Address                                    | <b>INST reg</b><br>Registers are explicitly specified as operands. Rarely used, HCS12<br>prefers implicit register addresses. |                                   |  |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|

| Example: $X=D (D \rightarrow X)$                                  | TFR D, X Copy value of register D to register X                                                                               |                                   |  |

| Implicit<br>(Register) Address<br>Freescale term:<br>Inherent INH | INST<br>The operand (one of the registers A, B, D, X, Y, SP) is contained im-<br>plicitly in the instruction mnemonic.        |                                   |  |

| Example: X++                                                      | INX                                                                                                                           | Increment the value of register X |  |

Memory variable operand

| Direct Address              | INST address                                                                                                                                                                  |                                        |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| DIR 8bit, EXT 16bit Address | The operand's memory address is part of the instruction. Program-<br>mers typically use variable names rather than addresses The address<br>will be assigned by the compiler. |                                        |

| Example: D=*0x2000          | LDD $2000 (no Hash)$ Load D with the value at memory address $2000_h$                                                                                                         |                                        |

| D = var1                    | LDD var1                                                                                                                                                                      | Load D with the value of variable var1 |

## *Constant operands* Warning: Without #... const would be an address rather than a constant!

| Immediate Operand INST                                                                                            |          | INST #const                                                                                                                        |                                          |

|-------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Immediate IMM The operand is part of the instruction. Constants must be m<br>#, e.g. #20, #–20, #\$0A, #%01101011 |          |                                                                                                                                    |                                          |

| Example:                                                                                                          | D=0xB010 | LDD #\$B010<br>(with Hash!) Load constant B010 <sub>h</sub> into register D<br>immediate for source operand, dest. operand implici |                                          |

|                                                                                                                   | D= &var1 | LDD #var1                                                                                                                          | Load D with the address of variable var1 |

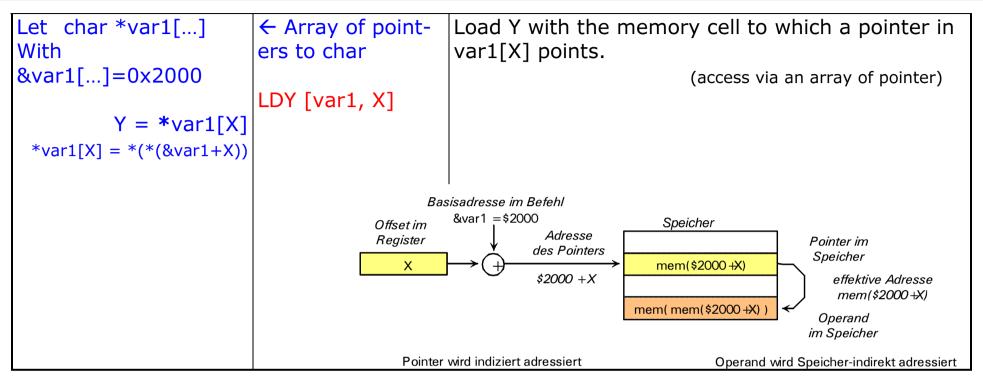

| Indirect Address in various variants (Motorola/Freescale term: Indexed) |                                                                                                                                                                                                                                                                                         |                                                                                            |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Register-indirect                                                       | INST 0, reg <sub>X,Y,SP</sub>                                                                                                                                                                                                                                                           |                                                                                            |

| Indexed IDX                                                             | Memory address in                                                                                                                                                                                                                                                                       | register X, Y, SP, i.e. register used as pointer                                           |

| Example: $D = *X$                                                       | LDD 0, X Load register D with the value at memory address in X ( <b>indirect address</b> )                                                                                                                                                                                              |                                                                                            |

| with Pre- or Post-<br>Increment or Dec-<br>rement<br>Auto Increment IDX | <b>INST</b> const $_{1,,+8}$ , $\{+ -\}reg_{X,Y,SP}$<br><b>INST</b> const $_{1,,+8}$ , $reg_{X,Y,SP}\{+ -\}$<br>The pointer in register X, Y, SP will be incremented or decremented<br>by some constant 1,, 8 before (pre) or after (post) using the<br>pointer to address the operand. |                                                                                            |

| X = X - 2; D =*X                                                        | LDD 2, -X                                                                                                                                                                                                                                                                               | Load memory value, to which X points, into regis-<br>ter D, decrement X by 2 <b>before</b> |

| D = *X; X = X + 4                                                       | LDD 4, X+                                                                                                                                                                                                                                                                               | , increment X by 4 afterwards                                                              |

| with index/offset                                                                       | INST const, re                                                                                                                                                                                                                                         | $g_{X,Y,SP,PC}$ address = const +reg <sub>X,Y,SP,PC</sub>                                                                                                                                                    |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Indexed<br>IDX 5bit constant                                                            | INST reg <sub>A,B,D</sub> , re                                                                                                                                                                                                                         | $g_{X,Y,SP,PC}$ address = $reg_{A,B,D}+reg_{X,Y,SP,PC}$                                                                                                                                                      |

| IDX1 9bit constant<br>IDX2 16bit constant                                               | The operand's address is the sum of a constant plus register X, Y or SP or the sum of two registers A, B or D plus X, Y or SP.                                                                                                                         |                                                                                                                                                                                                              |

| Example:<br>Let char var1[]<br>with &var1=0x2000<br>Y = var1[X]<br>var1[X] = *(&var1+X) | ← array of char<br>LDY var1, X<br>(instead of var1 any 16bit<br>constant possible                                                                                                                                                                      | Load Y with var1[X], i.e. the value at memory ad-<br>dress var1 + X (indexing array var1 by index X)<br>base address in instruction<br>offset in &var1 = \$2000<br>register<br>X + \$2000 + X memory operand |

| Y = *(D+X)                                                                              | LDY D, X                                                                                                                                                                                                                                               | Load Y with contents of memory address D + X                                                                                                                                                                 |

| Memory-indirect<br>with index                                                           | INST [const, $reg_{X,Y,SP,PC}$ ]<br>INST [D, $reg_{X,Y,SP,PC}$ ]                                                                                                                                                                                       |                                                                                                                                                                                                              |

| Indexed-Indirect<br>[ IDX2 ]                                                            | The operand's memory address is in a pointer in memory. This memory address will be addressed via another pointer, which is cal-<br>culated as the value of register X, Y, SP or PC plus a constant or reg-<br>ister D (Note: A, B not allowed here!). |                                                                                                                                                                                                              |

| Example:<br>Y = *(*(D+X))                                                               | LDY [D, X]                                                                                                                                                                                                                                             | Load Y with the value of the memory cell, to which the memory pointer points, to which D+X point                                                                                                             |

Branch instructions use so called **relative addressing** (Motorola/ Freescale-name REL). Relative addresses use the current value of the instruction pointer and add a constant offset, which is included in the instruction. The programmer need not care about details, but simply uses a label as the target of the branch:

#### start: . . . BRA start

Unfortunately, normal branches limit the offset to 8bit. However, there is a Long Branch version LBRA using a 16bit offset (see chapter 2.6).

# **2.4 Data Transport Instructions**

# 2.4 Instruction Set 1: Data Transport (see [2.1 Chapter 2.9], [3.1 Chapter 5, 6])

- Data transport instructions (including stack)

- Arithmetic and logic instructions

- Compare and branch instructions (including software interrupts)

- Miscellaneous instructions

## Abbreviations

| reg <sub>A,B,D</sub> | One of the registers A, B, D,                                                       |  |

|----------------------|-------------------------------------------------------------------------------------|--|

| mem                  | Memory operand with arbitrary memory addressing (direct, indexed, indirect-indexed) |  |

| imm                  | Immediate operand                                                                   |  |

| mem_i                | mem Or imm                                                                          |  |

| adr                  | Code address relative to PC                                                         |  |

| $LD{AA AB  S}$       | Abbreviation for LDAA, LDAB or LDS                                                  |  |

| 8bit Or 16bit        | Used as index: Size of an operand                                                   |  |

If not stated otherwise, all instructions do modify CCR status bits N, Z, V, C depending on the instruction's result such that conditional branch instructions can be used directly without a preceding compare instruction.

# **2.4 Data Transport Instructions**

| <b>Transport Instructions</b> (Status bits N, Z, V, C are modified by LD and ST instructions only) |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $LD{AA AB D X Y S} mem_i$ *2                                                                       | $\texttt{mem\_i} \rightarrow \texttt{reg}_{\texttt{A},\texttt{B},\texttt{D},\texttt{X},\texttt{Y},\texttt{SP}}$                                                                                                                                           | LoaD register from memory<br>A, B are loaded with an 8bit, D, X, Y,<br>SP are loaded with an 16bit value                                                                                          |

| $ST{AA AB D X Y S} mem$ *2                                                                         | $\texttt{reg}_{\texttt{A},\texttt{B},\texttt{D},\texttt{X},\texttt{Y},\texttt{SP}} \rightarrow \texttt{mem}$                                                                                                                                              | STore register to memory                                                                                                                                                                          |

| <pre>TFR reg<sub>A,B,D,X,Y,SP,CCR</sub> /</pre>                                                    | reg 	o reg                                                                                                                                                                                                                                                | TransFeR register to register<br>If the source register is 8bit and the<br>destination register is 16bit, the MS-<br>Byte will be loaded with the sign of<br>the Shit value (Sign Extension) Vice |

|                                                                                                    |                                                                                                                                                                                                                                                           | the 8bit value (Sign Extension). Vice versa only the LSByte will be copied.                                                                                                                       |

| <b>EXG</b> reg <sub>A,B,D,X,Y,SP,CCR</sub> ,<br>*1 reg <sub>A,B,D,X,Y,SP,CCR</sub>                 | $\texttt{reg}\leftrightarrow\texttt{reg}$                                                                                                                                                                                                                 | EXchanGe register<br>Swap register contents                                                                                                                                                       |

|                                                                                                    | $\mathbf{A} \rightarrow \mathbf{B} \text{ bzw. } \mathbf{B} \rightarrow \mathbf{A}$                                                                                                                                                                       | Variants of TFR and EXG                                                                                                                                                                           |

|                                                                                                    | $SP \rightarrow X, SP \rightarrow Y, X \rightarrow SP, Y \rightarrow SP$                                                                                                                                                                                  | (shorter opcodes)                                                                                                                                                                                 |

| -                                                                                                  | $A \rightarrow CCR, CCR \rightarrow A$<br>$D \leftrightarrow X, X \leftrightarrow D$                                                                                                                                                                      |                                                                                                                                                                                                   |

| MOVB mem_i, mem<br>MOVW mem_i, mem<br>*1                                                           | $\begin{array}{cccc} \texttt{mem\_i} \rightarrow \texttt{mem} & \texttt{8bit} \\ \texttt{mem\_i} \rightarrow \texttt{mem} & \texttt{16bit} \\ \texttt{Adressing [IDX], IDX1, IDX2 not possible,} \\ \texttt{for IDX only -16 +15 is allowed} \end{array}$ | MOVe Byte<br>MOVe Word<br>Direct memory to memory copy                                                                                                                                            |

| <b>SEX</b> reg <sub>A,B,CCR</sub> , reg <sub>D,X,Y,SP</sub> *1                                     | $reg_{A,B,C} \rightarrow reg_{D,X,Y,SP}$                                                                                                                                                                                                                  | Sign EXtension Copy<br>from 8bit to 16bit for 2s-comple-<br>ment-numbers (same as TFR)                                                                                                            |

$^{*1}$  These instruction do not modify status bits N, Z, V, C.

$^{\ast 2}$  These instructions do modify status bits N, Z, V, but not C !

#### Calculate a pointer (indexed or indirect address = effective address)

| $LEA{X Y S} mem$ | $Address \text{ of } \mathtt{mem} \to \mathtt{reg}_{\mathtt{X}, \mathtt{Y}, \mathtt{SP}}$ | Load Effective memory Ad-             |

|------------------|-------------------------------------------------------------------------------------------|---------------------------------------|

| . 1              |                                                                                           | dress into register                   |

|                  |                                                                                           | Note: Calculation is done during run- |

|                  |                                                                                           | time, not compile time                |

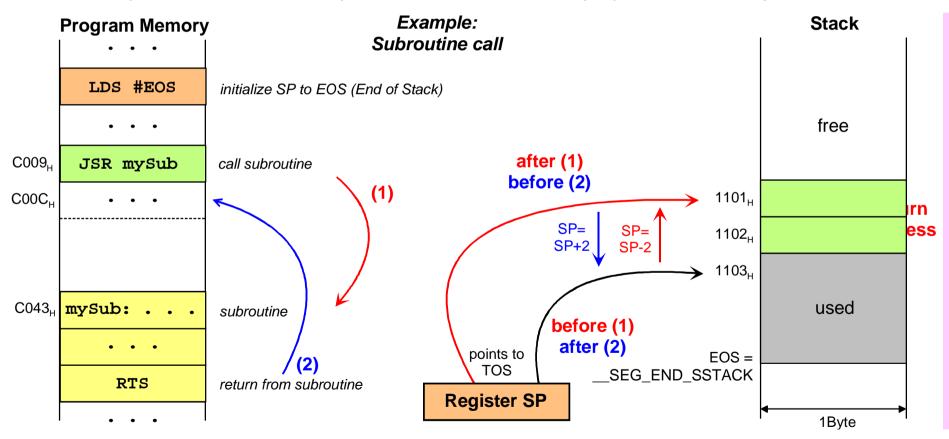

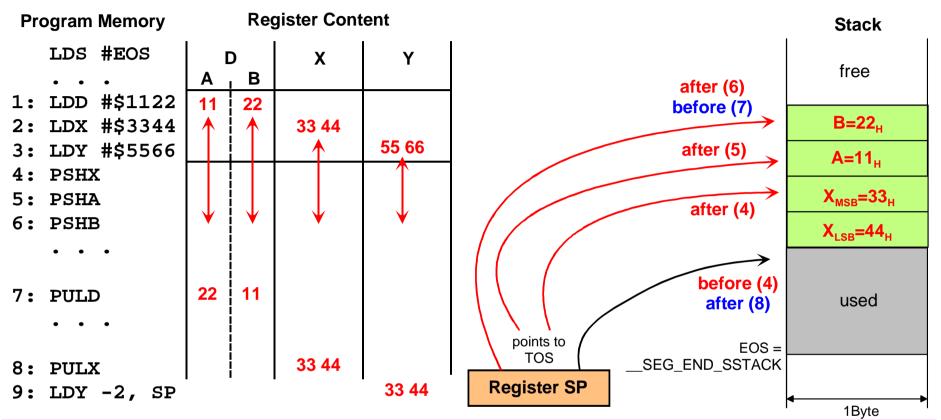

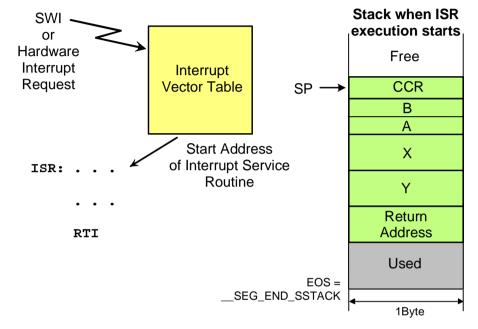

Stack (see chapter 2.6)

|                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                 | PuSH register to stack<br>Copy register on stack        |

|-----------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

|                 |                                                                                                                      | Pull register from stack<br>Copy from stack to register |

| $PUL{D X Y} *1$ | $\texttt{Stack} \rightarrow \texttt{reg}_{\texttt{D},\texttt{X},\texttt{Y}},  \texttt{SP+2} \rightarrow \texttt{SP}$ | copy from stack to register                             |

<sup>\*1</sup> These instructions (except **PULC**) do not modify status bits N, Z, V, C.

#### Note:

PSH... und PUL... can be substituted by ST... and LD...:

| E.g.:        | STAA 1    | , -SP      | =    | PSHA                          |                                |

|--------------|-----------|------------|------|-------------------------------|--------------------------------|

|              | STD 2     | , -SP      | =    | PSHD                          |                                |

|              | LDAA 1    | , SP+      | =    | PULA                          |                                |

|              | LDD 2     | , SP+      | =    | PULD                          |                                |

| Modification | of the st | ack pointe | rsp  | without actually copying data | a (required in chapter 4):     |

|              | LEAS n    | , -SP      | Allc | cate stack space for n byte   | (LEAS n, $-SP = LEAS -n$ , SP) |

|              | LEAS n    | , +SP      | Fre  | e n Byte from stack           | (LEAS n, SP = LEAS n, +SP)     |

|              |           |            |      |                               |                                |

| Example Program 1              |            | (CodeWarrior project AsmIntro.mcp)                               |                         |

|--------------------------------|------------|------------------------------------------------------------------|-------------------------|

| .data: SECTION<br>var1: ds.w 1 |            | ; Global variables in RAM (uninitialized)<br>; short var1        |                         |

| var1. di<br>var2: di           |            | ; char var2                                                      |                         |

| var3: da                       |            | ; char var3[2]                                                   |                         |

| .const: SI<br>const1: de       |            | ; Global constants in ROM (initi<br>\$22, \$33 ; const char cons |                         |

|                                | ECTION     | ; Program code (Address mo                                       | de of explicit operand) |

|                                | DD #\$1234 | ; D = 0x1234                                                     | (immediate)             |

| TI                             | FR D, X    | ; $X = D = 0x1234$                                               | (register)              |

| S                              | TD var1    | ; $var1 = D = 0x1234$                                            | (direct)                |

| S                              | TAA var2   | ; $var2 = A = 0x12$                                              |                         |

| S                              | TD var3    | ; $var3 = D$ with $var3[0] = 0x1$                                | 12, var3[1]= 0x34       |

| LI                             | DD const1  | ; $D = const1 = 0x0011$                                          | (direct)                |

| LI                             | DD #const1 | ; D = &const1                                                    | (immediate)             |

| Continued |           | ; D=&const1 (from previous instruction)                 |                                  |  |

|-----------|-----------|---------------------------------------------------------|----------------------------------|--|

| LDY :     | #\$0001   | ; $Y = 0 \times 0001$                                   | (immediate)                      |  |

| LDX 1     | D, Y      | ; X = *(D+Y) = *(&const1+1) = 0x1122 (indexed)          |                                  |  |

| LDX (     | const1, Y | ; $X = const1[Y] = 0x1122$                              | (indexed) const1[Y]=*(&const1+Y) |  |

| LDY :     | #const1   | ; Y = &const1                                           |                                  |  |

| LDAA      | 1, Y+     | ; $A = *Y = 0$                                          | (indirect with post-increment)   |  |

|           |           | ; <b>Y</b> = <b>Y</b> +1 = &const1[1]                   |                                  |  |

| LDAA      | 2, +Y     | ; Y = Y+2 = &const1[3]                                  |                                  |  |

|           |           | ; $A = *Y = 0x33$                                       | (indirect with pre-increment)    |  |

| LDAA      | 1, -Y     | ; <b>Y = Y-1</b> = &const1[2]                           |                                  |  |

|           |           | ; <b>A</b> = <b>*Y</b> = 0x22                           | (indirect with pre-decrement)    |  |

| LDAA      | 1, Y-     | ; <b>A</b> = <b>*Y</b> = 0x22                           | (indirect with post-decrement)   |  |

|           |           | ; <b>Y = Y-1</b> = &const1[1]                           |                                  |  |

| LDD       | #const1   | ; D = &const1                                           |                                  |  |

| STD       | var1      | ;                                                       |                                  |  |

| LDX       | #0000     | ; X = 0                                                 |                                  |  |

| LDD       | var1, X   | ; D = var1[X] = *(&var1+X) =                            | &const1 (indexed)                |  |

| LDD       | [var1, X] | ; D = *var1[X]= *(*(&var1+X))= 0x0011(indirect indexed) |                                  |  |

Continued

| LDD  | #\$AAAA     | ; $D = 0 \times A A A A$                                   |

|------|-------------|------------------------------------------------------------|

| LDX  | #\$5555     | ; $X = 0x5555$                                             |

| LDAA | #\$7F       | ; $A = 0 \times 7F$                                        |

| TFR  | A, X        | ; $X = A = (sign extended) 7Fh = 0x007F$                   |

| LDAA | #\$80       | ; $A = 0 \times 80$                                        |

| TFR  | A, X        | ; $X = A = sign extended 80h = 0xFF80$                     |

| TFR  | Х, В        | ; $B = X_{LSB} = 0 \times 80$                              |

| MOVW | #\$5678,var | $x_1; var1 = 0x5678$                                       |

| MOVW | var1, var2  | ; var2 =0x56, but note: var3[0] = 0x78 will be overwritten |

| LDX  | #var3       | ; X = &var3                                                |

| MOVB | var1, 0,X   | ; *X = var3[0] = MSB of var1 = 0x56                        |

| MOVB | 0,X, 1,X    | ; $var3[1] = var3[0] = 0x5656$                             |

| תת ז |             | ; $D = var1 = 0x5678$                                      |

| LDD  | Vari        | , D = Val 1 = 0.00070                                      |

| LDD  | var1+1      | ; $D = (LSByte of var1, MSByte of var2) = 0x7856$          |

| LDD  | var1+3      | ; $D = (var3[0], var3[1]) = 0x5656$                        |

## **2.5 Instruction Set 2: Arithmetic and Logic Operations**

Add, Subtract, Increment, Decrement, Invert Sign

| $B+A \rightarrow A, B+X \rightarrow X, B+Y \rightarrow Y$                                                                                                            | ADD/SuBtract                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $A - B \rightarrow A$                                                                                                                                                | (A, B are loaded with a 8bit, D, X, Y, are loaded with a 16bit value)                                                                                                                                                                                                                                                                                                                                                          |

| $\texttt{reg}_{\texttt{A},\texttt{B},\texttt{D}} + \texttt{mem}_\texttt{i} \rightarrow \texttt{reg}_{\texttt{A},\texttt{B},\texttt{D}}$                              | ADD 8bit ±8bit or 16bit ±16bit                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\texttt{reg}_{\texttt{A},\texttt{B},\texttt{D}}-\texttt{mem}_{\texttt{i}} \rightarrow \texttt{reg}_{\texttt{A},\texttt{B},\texttt{D}}$                              | SUBtract                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $\mathtt{reg}_{\mathtt{A},\mathtt{B}} + \mathtt{mem} + \mathtt{C} \rightarrow \mathtt{reg}_{\mathtt{A},\mathtt{B}}$                                                  | ADd with Carry 8bit                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\mathtt{reg}_{\mathtt{A},\mathtt{B}}$ - mem - C $\rightarrow \mathtt{reg}_{\mathtt{A},\mathtt{B}}$                                                                  | SuBtract with Carry 8bit                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\texttt{mem+1} \rightarrow \texttt{mem}$                                                                                                                            | INCrement memory 8bit                                                                                                                                                                                                                                                                                                                                                                                                          |

| $reg_{A,B,X,Y,S}+1 \rightarrow reg_{A,B,X,Y,S}$                                                                                                                      | INcrement register                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\texttt{mem-l} \rightarrow \texttt{mem}$                                                                                                                            | DECrement memory 8bit                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\texttt{reg}_{\texttt{A},\texttt{B},\texttt{X},\texttt{Y},\texttt{S}}\texttt{-1} \rightarrow \texttt{reg}_{\texttt{A},\texttt{B},\texttt{X},\texttt{Y},\texttt{S}}$ | DEcrement register                                                                                                                                                                                                                                                                                                                                                                                                             |

| $0 \rightarrow \texttt{mem}$                                                                                                                                         | CLeaR byte                                                                                                                                                                                                                                                                                                                                                                                                                     |

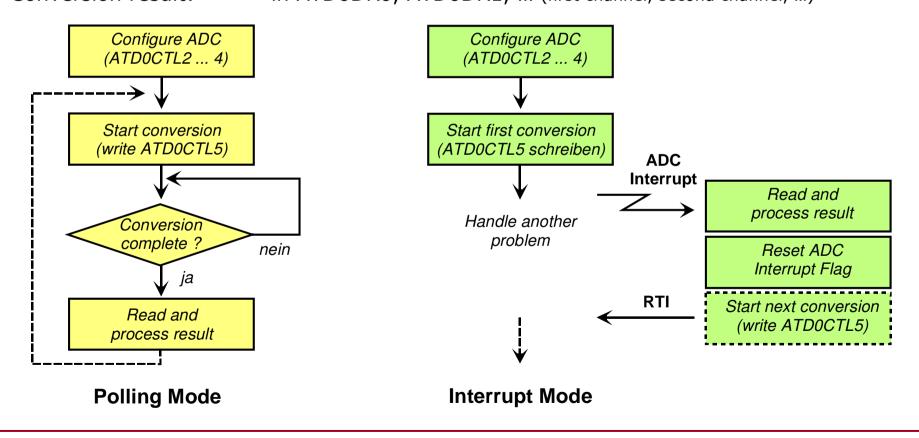

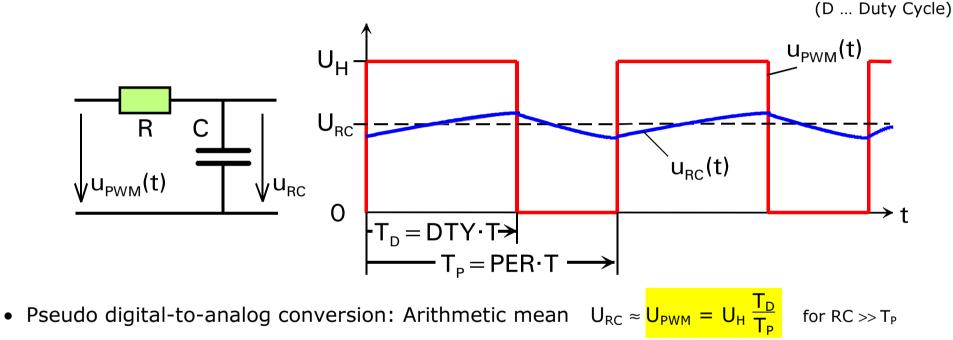

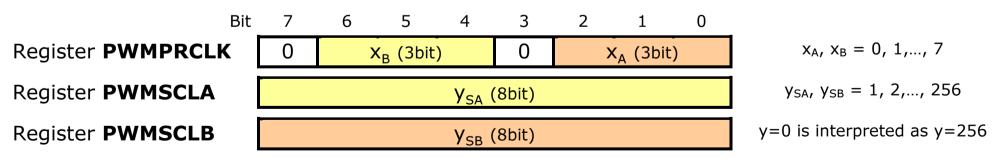

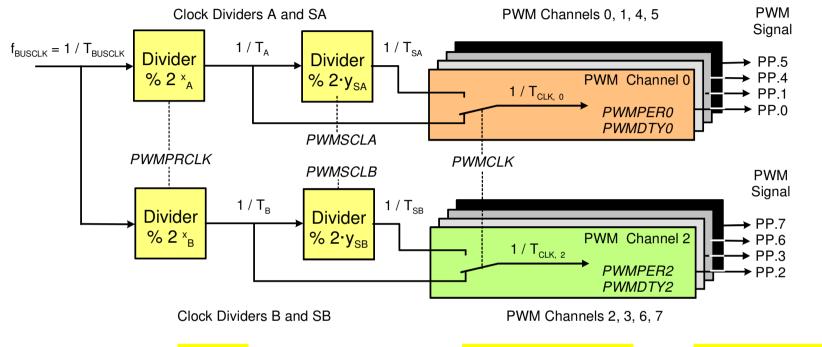

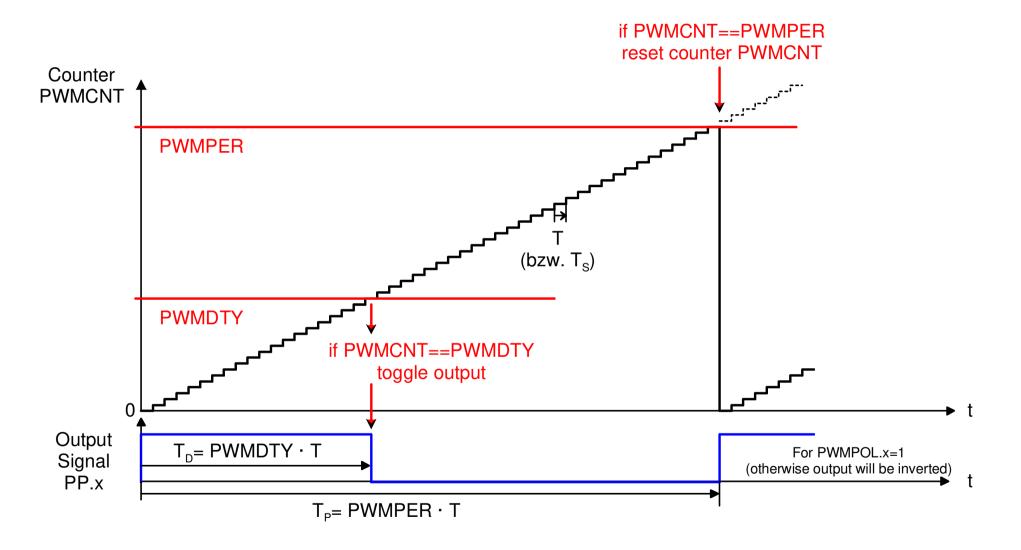

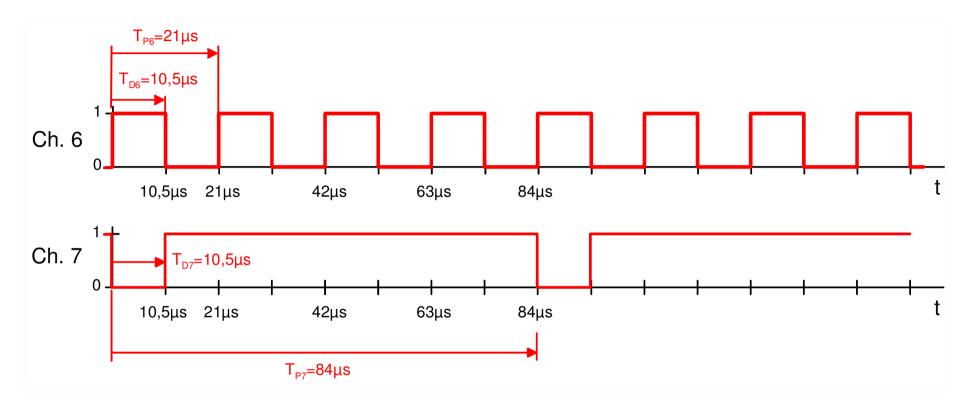

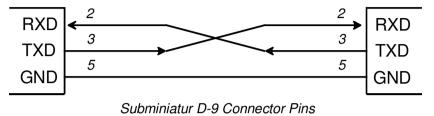

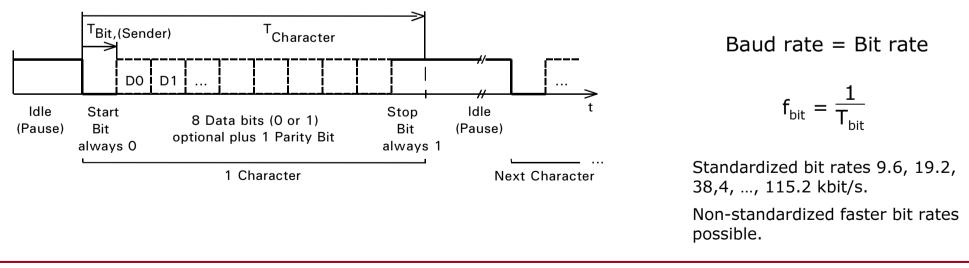

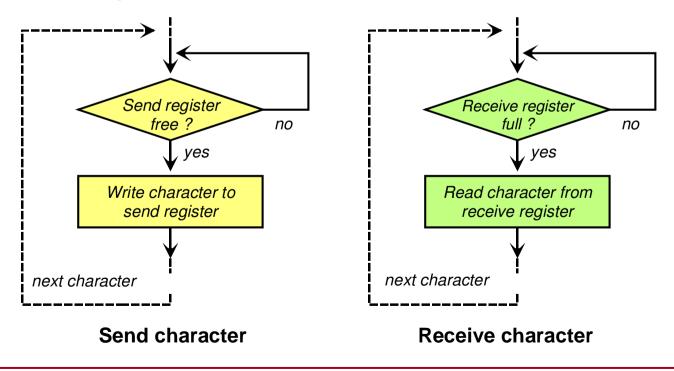

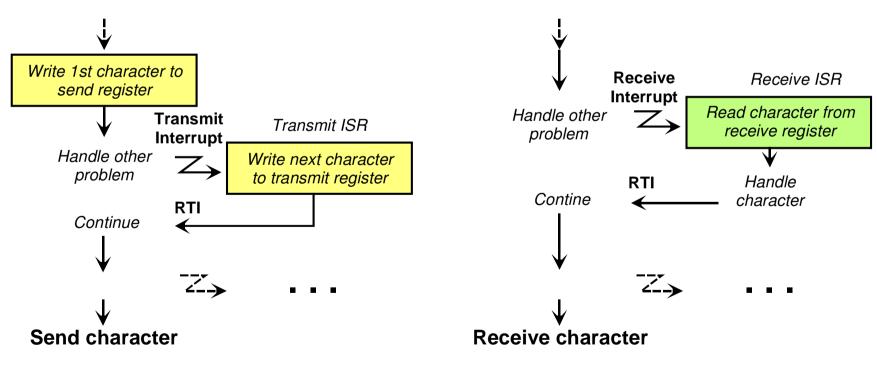

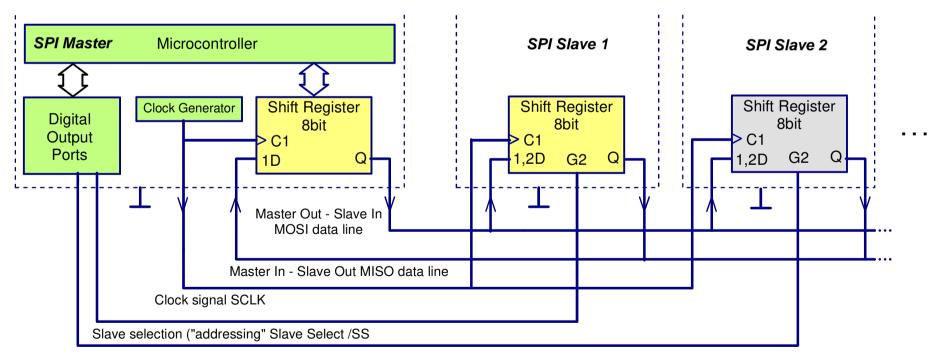

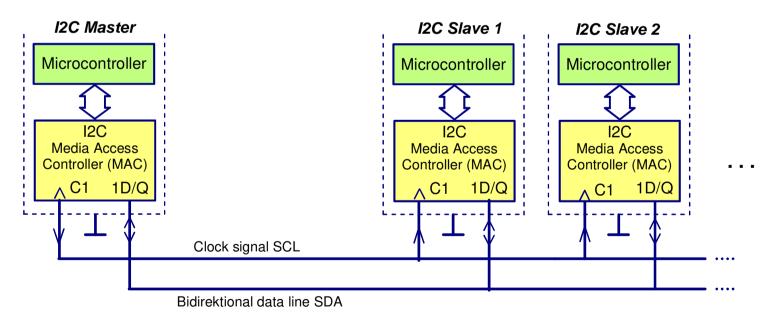

| $0 \rightarrow \texttt{reg}_{\texttt{A},\texttt{B}}$                                                                                                                 | (Load with 0)                                                                                                                                                                                                                                                                                                                                                                                                                  |